Hi, I’m using zig to build a C project (see here Static linking newlibc as libc, freestanding on ARM, zig + c libraries - #2 by simoneruffini) and I’m having a lot of troubles.

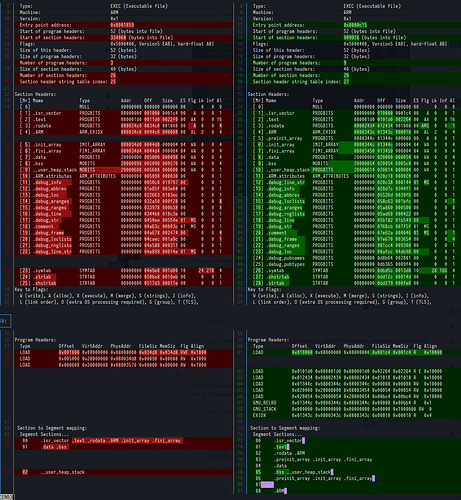

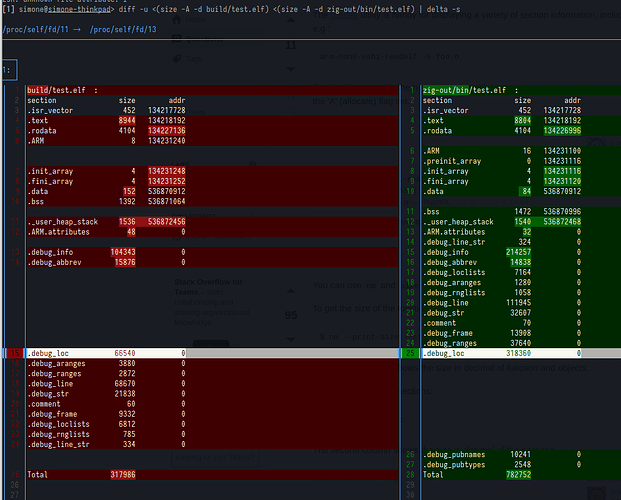

I’m trying to debug the process step by step and first I want to understand how zig is building my source files. I’m able to compile the project but I’m getting a huge binary output file.

ll build/test.elf zig-out/bin/test.elf ~/Documents/test/stm32f446re

-rwxr-xr-x 1 simone simone 328K 8 feb 22.36 build/test.elf

-rwxr-xr-x 1 simone simone 1,1M 9 feb 11.50 zig-out/bin/test.elf

So I took a look at the intermediate compilation units object files and their sizes. With respect to the ones build by gcc they are sometimes smaller but other times a lot bigger:

:r !ls -al ./build/main.o zig-cache/o/9e04bf4154200a9ad229a98adf1ef133/main.o

-rw-r--r-- 1 simone simone 30288 8 feb 22.35 ./build/main.o

-rw-r--r-- 1 simone simone 35228 8 feb 22.59 zig-cache/o/9e04bf4154200a9ad229a98adf1ef133/main.o

:r !ls -al ./build/MedianFilter.o zig-cache/o/608588b52ad424e39fbe7b754bc2d13b/MedianFilter.o

-rw-r--r-- 1 simone simone 5372 8 feb 22.35 ./build/MedianFilter.o

-rw-r--r-- 1 simone simone 9328 8 feb 22.59 zig-cache/o/608588b52ad424e39fbe7b754bc2d13b/MedianFilter.o

:r !ls -al ./build/stm32f4xx_it.o zig-cache/o/8556142a4e8cb3a64acad0a21c600e20/stm32f4xx_it.o

-rw-r--r-- 1 simone simone 5268 8 feb 22.35 ./build/stm32f4xx_it.o

-rw-r--r-- 1 simone simone 4896 8 feb 22.59 zig-cache/o/8556142a4e8cb3a64acad0a21c600e20/stm32f4xx_it.o

:r !ls -al ./build/stm32f4xx_hal_msp.o zig-cache/o/88e82eefb964b9cc17f8339c485391dd/stm32f4xx_hal_msp.o

-rw-r--r-- 1 simone simone 13776 8 feb 22.35 ./build/stm32f4xx_hal_msp.o

-rw-r--r-- 1 simone simone 13568 8 feb 22.59 zig-cache/o/88e82eefb964b9cc17f8339c485391dd/stm32f4xx_hal_msp.o

:r !ls -al ./build/stm32f4xx_hal_tim.o zig-cache/o/99288ce3e59a0a256c3a994803be2af0/stm32f4xx_hal_tim.o

-rw-r--r-- 1 simone simone 153896 8 feb 22.35 ./build/stm32f4xx_hal_tim.o

-rw-r--r-- 1 simone simone 236464 8 feb 22.59 zig-cache/o/99288ce3e59a0a256c3a994803be2af0/stm32f4xx_hal_tim.o

:r !ls -al ./build/stm32f4xx_hal_tim_ex.o zig-cache/o/3392d5d156564ae16d92e6e1e61287dd/stm32f4xx_hal_tim_ex.o

-rw-r--r-- 1 simone simone 61536 8 feb 22.35 ./build/stm32f4xx_hal_tim_ex.o

-rw-r--r-- 1 simone simone 93924 8 feb 22.59 zig-cache/o/3392d5d156564ae16d92e6e1e61287dd/stm32f4xx_hal_tim_ex.o

:r !ls -al ./build/stm32f4xx_hal_uart.o zig-cache/o/f45f1e22a18dfeb915af7d502fe65480/stm32f4xx_hal_uart.o

-rw-r--r-- 1 simone simone 116424 8 feb 22.35 ./build/stm32f4xx_hal_uart.o

-rw-r--r-- 1 simone simone 110272 8 feb 22.59 zig-cache/o/f45f1e22a18dfeb915af7d502fe65480/stm32f4xx_hal_uart.o

:r !ls -al ./build/stm32f4xx_hal_rcc.o zig-cache/o/dfc9ef3cafd45a08e1748e5daf7d89c1/stm32f4xx_hal_rcc.o

-rw-r--r-- 1 simone simone 22404 8 feb 22.35 ./build/stm32f4xx_hal_rcc.o

-rw-r--r-- 1 simone simone 29416 8 feb 22.59 zig-cache/o/dfc9ef3cafd45a08e1748e5daf7d89c1/stm32f4xx_hal_rcc.o

:r !ls -al ./build/stm32f4xx_hal_rcc_ex.o zig-cache/o/dd46e027c458622b9f55f8559f13606c/stm32f4xx_hal_rcc_ex.o

-rw-r--r-- 1 simone simone 32904 8 feb 22.35 ./build/stm32f4xx_hal_rcc_ex.o

-rw-r--r-- 1 simone simone 49076 8 feb 22.59 zig-cache/o/dd46e027c458622b9f55f8559f13606c/stm32f4xx_hal_rcc_ex.o

:r !ls -al ./build/stm32f4xx_hal_flash.o zig-cache/o/7ec7a26337c091e4b5b68b21fca20066/stm32f4xx_hal_flash.o

-rw-r--r-- 1 simone simone 17144 8 feb 22.35 ./build/stm32f4xx_hal_flash.o

-rw-r--r-- 1 simone simone 17440 8 feb 22.59 zig-cache/o/7ec7a26337c091e4b5b68b21fca20066/stm32f4xx_hal_flash.o

:r !ls -al ./build/stm32f4xx_hal_flash_ex.o zig-cache/o/efd3655fa5f8371e61870ae4070e0039/stm32f4xx_hal_flash_ex.o

-rw-r--r-- 1 simone simone 22280 8 feb 22.35 ./build/stm32f4xx_hal_flash_ex.o

-rw-r--r-- 1 simone simone 22092 8 feb 22.59 zig-cache/o/efd3655fa5f8371e61870ae4070e0039/stm32f4xx_hal_flash_ex.o

:r !ls -al ./build/stm32f4xx_hal_flash_ramfunc.o zig-cache/o/e575702641443b72ac5f71bcd076bb7e/stm32f4xx_hal_flash_ramfunc.o

-rw-r--r-- 1 simone simone 6220 8 feb 22.35 ./build/stm32f4xx_hal_flash_ramfunc.o

-rw-r--r-- 1 simone simone 5608 8 feb 22.59 zig-cache/o/e575702641443b72ac5f71bcd076bb7e/stm32f4xx_hal_flash_ramfunc.o

:r !ls -al ./build/stm32f4xx_hal_gpio.o zig-cache/o/8bd73bf66e49c02b4de785fa40745d3d/stm32f4xx_hal_gpio.o

-rw-r--r-- 1 simone simone 14472 8 feb 22.35 ./build/stm32f4xx_hal_gpio.o

-rw-r--r-- 1 simone simone 16064 8 feb 22.59 zig-cache/o/8bd73bf66e49c02b4de785fa40745d3d/stm32f4xx_hal_gpio.o

:r !ls -al ./build/stm32f4xx_hal_dma_ex.o zig-cache/o/320697216849f57288f06ee30b883927/stm32f4xx_hal_dma_ex.o

-rw-r--r-- 1 simone simone 17432 8 feb 22.35 ./build/stm32f4xx_hal_dma_ex.o

-rw-r--r-- 1 simone simone 41084 8 feb 22.59 zig-cache/o/320697216849f57288f06ee30b883927/stm32f4xx_hal_dma_ex.o

:r !ls -al ./build/stm32f4xx_hal_dma.o zig-cache/o/d8005e7182f54a18ef4f67f4611b352e/stm32f4xx_hal_dma.o

-rw-r--r-- 1 simone simone 26436 8 feb 22.35 ./build/stm32f4xx_hal_dma.o

-rw-r--r-- 1 simone simone 36356 8 feb 22.59 zig-cache/o/d8005e7182f54a18ef4f67f4611b352e/stm32f4xx_hal_dma.o

:r !ls -al ./build/stm32f4xx_hal_pwr.o zig-cache/o/b47ab7db75a3fa4f15862b8bf641f383/stm32f4xx_hal_pwr.o

-rw-r--r-- 1 simone simone 12296 8 feb 22.35 ./build/stm32f4xx_hal_pwr.o

-rw-r--r-- 1 simone simone 14244 8 feb 22.59 zig-cache/o/b47ab7db75a3fa4f15862b8bf641f383/stm32f4xx_hal_pwr.o

:r !ls -al ./build/stm32f4xx_hal_pwr_ex.o zig-cache/o/01e7e5906a3cfce5eb6706ad53b571b8/stm32f4xx_hal_pwr_ex.o

-rw-r--r-- 1 simone simone 13128 8 feb 22.36 ./build/stm32f4xx_hal_pwr_ex.o

-rw-r--r-- 1 simone simone 12496 8 feb 22.59 zig-cache/o/01e7e5906a3cfce5eb6706ad53b571b8/stm32f4xx_hal_pwr_ex.o

:r !ls -al ./build/stm32f4xx_hal_cortex.o zig-cache/o/e5b65b2fa6b1256cab359bf320787ca0/stm32f4xx_hal_cortex.o

-rw-r--r-- 1 simone simone 26452 8 feb 22.36 ./build/stm32f4xx_hal_cortex.o

-rw-r--r-- 1 simone simone 29120 8 feb 22.59 zig-cache/o/e5b65b2fa6b1256cab359bf320787ca0/stm32f4xx_hal_cortex.o

:r !ls -al ./build/stm32f4xx_hal.o zig-cache/o/1696de14f92d2c979677719783df1848/stm32f4xx_hal.o

-rw-r--r-- 1 simone simone 20352 8 feb 22.36 ./build/stm32f4xx_hal.o

-rw-r--r-- 1 simone simone 21256 8 feb 22.59 zig-cache/o/1696de14f92d2c979677719783df1848/stm32f4xx_hal.o

:r !ls -al ./build/stm32f4xx_hal_exti.o zig-cache/o/47c1c46543fadda6325e01461f19c71c/stm32f4xx_hal_exti.o

-rw-r--r-- 1 simone simone 12620 8 feb 22.36 ./build/stm32f4xx_hal_exti.o

-rw-r--r-- 1 simone simone 14124 8 feb 22.59 zig-cache/o/47c1c46543fadda6325e01461f19c71c/stm32f4xx_hal_exti.o

:r !ls -al ./build/system_stm32f4xx.o zig-cache/o/458200b72dc662e8df51c6bf2e572a28/system_stm32f4xx.o

-rw-r--r-- 1 simone simone 7388 8 feb 22.36 ./build/system_stm32f4xx.o

-rw-r--r-- 1 simone simone 7292 8 feb 22.59 zig-cache/o/458200b72dc662e8df51c6bf2e572a28/system_stm32f4xx.o

:r !ls -al ./build/startup_stm32f446xx.o zig-cache/o/34deb1aa406cbf5da07069ba8d251c04/startup_stm32f446xx.o

-rw-r--r-- 1 simone simone 7284 8 feb 22.36 ./build/startup_stm32f446xx.o

-rw-r--r-- 1 simone simone 7108 8 feb 22.59 zig-cache/o/34deb1aa406cbf5da07069ba8d251c04/startup_stm32f446xx.o

Why is this happening? how can I understand what the llvm compiler is adding that the gcc one is not?

I tried comparing the object files with objdump but the symbols are all unsorted so I can’t compare one to one those files. Do you have any suggestions?

(on a side not what is the correct way to get a verbose output from zig build: I see there is zig build --verbose that is doing nothing in particular, then exe.setVerboseLink(true) and b.verbose = true , b.verbose_cc=true… where b is the parameter of pub fn build())