Writing a xv6 port to zig and ran into an issue with the uart0 not being able to take in keyboard inputs. Ive tested it manually but for some reason the actual keyboard isn’t working. anyone implement it before or know how to debug it?

Don’t forget to mark the pointers volatile when you reference memory mapped I/O.

const io_ptr: *volatile u8 = @ptrFromInt(0x12345678);

What machine are you emulating with qemu?

I get interrupts but i dont get keyboard input data

I assume that you use the virt board.

The sources are: qemu/hw/riscv/virt.c at master · qemu/qemu · GitHub

From that file: UART0 is memory mapped and the base address is 0x10000000

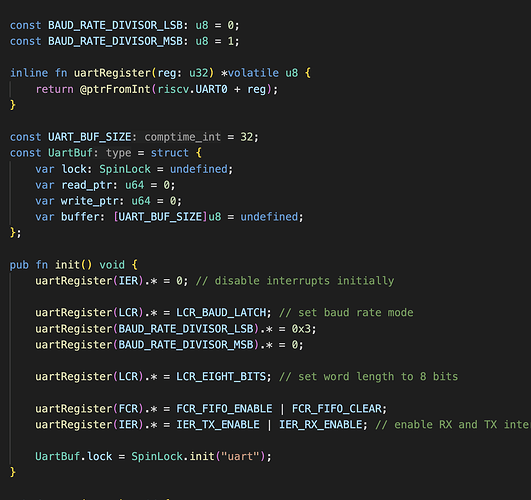

The uart chip is ns16550a, it is the original ibm pc uart. There are 8 registers, the first (in the base address) is for reading/writing the uart bytes. For sure you must initialize some registers (for 8 bits, 1 stop bit, rate, etc.).

The registers are:

| Address | Name | Description |

|---|---|---|

| base+0 | rxd/txd | Receive/Transmitt data |

| base+1 | ier | Interrupt enable |

| base+2 | fcr | FIFO control |

| base+3 | lcr | Line control |

| base+4 | mcr | Modem control |

| base+5 | lsr | Line status |

| base+6 | msr | Modem status |

| base+7 | scr | Scratch Pad |

There is GitHub - tzx/nOSering: Attempt on RISC-V Operating System in Zig

Amazing uart info: Serial UART, an in depth tutorial - Lammert Bies

uart implementation in zig: nOSering/src/uart.zig at main · tzx/nOSering · GitHub

blog post: Timmy Xiao

yep ive looked at all of those and emailed lammert, in that implementation he doesn’t actually get uart input but I’ve tried his config

found the bug was not in qemu, a interrupt enable bit wasn’t being set in my trap handler